IELS3012: Innvevde systemer

Introduksjon

Tidligere har vi jobbet en del med mikrokontrollere i innebygde systemer. Vi har jobbet med RTOS, (Real Time Operating System) som gjør at vi kan lage enda mer tidskritiske applikasjoner. Nå gjenstår det å dyppe å programmerbare kretser. Vi jobber enda mer spesifikt med Field Programmable gate Array (FPGA). Disse er kretser hvor man kan bestemme programvaren. PLA og PAL er eksempler på tidlige programmerbare kretser som kunne implementereenkel kombinatorisk logikk. Bildet viser en funksjon y implementert i et Programmable Logic Array(PLA).

NB: Må ikke forveksles med Applikasjonsspesifikke Integreerte Kretser (ASIC), som også designes med et HDL, men som ikke kan endres etter de er produserte.

Hvorfor bruker vi programmerbare kretser?

Mikrokontrollere er billige, ganske fleksible, kan designes til å være veldig strømgerrige og er enkle bruk. Ulemper med mikrokontrollere er at de er sekvensielle, og har en begrenset beregningshastighet. De har sjeldent mulig til å håntere store mengder data og er laget til å være veldig generelle, som på den ene sisten gjør de allsidige, men de kan ikke brukes til mer spesialiserte applikasjoner.

Spesielt i systemer som video- og lydprosessering (grafikk), kryptografi og AI (matriseoperasjoner) er det viktig å designe systemer som er rustet til å håndtere større mengde beregnnger.

Programmerbare kretser er brikker hvor maskinvaren kan programmeres.

Fordeler med disse er at de er svært fleksible, og egnet til en lang rekke applikasjoner. De er raske og er gode for å implementere parallelisering. Ulempene med disse er at de er relativt dyre, mer komplekse og har høyere strømforbruk.

Hvordan virker en FPGA?

I programmerbare kretser beskriver man sammenhengen av kretselemeter for å få gitt oppførsel. I et system som designes vil man forklare den overordnede strukturen til systemet, med grensensittet, og så beskrive hver individuelle del av systemet. man skriver kode som beskriver systemet, og syntesiserer dette. Dette betyr at koden tolkes og de gitte kretselementene implementeres. Vi analyserer så systemet om det gir gitt ønsket oppførsel i en iterativ prosess.

Dette gjør vi som oftest med Registeroverføringsnivå, "Register-transfer Level (RTL), et abstraksjonsnivå hvor vi representerer et system med kombinatorisk logikk og vipper(registre).

Et digitalt system har et grensensitt, moduler og forbindelser mellom disse modulene. De kan beskrives med deres grensensitt (entity), deres moduler og oppførsel (architecture) og sammenkoblingen mellom moduler(structural). Designet er hierarkisk bygd opp slik at hver modul igjen har sitt grensesnitt og oppførselskode eller eventuelt sammenkobling av moduler med sine grensesnitt og oppførselskode.

Vi bruker maskinbeskrivende språk (HDL, Hardware Description Language) til å beskrive elektroniske systemer. Det er ikke et programmeringsspråk, men et kodespråk. Dette er pga man ikke lager et program, men beskriver heller den fysiske programvaren. De mest utbredte HDL-språkene er VHDL og Verilog. Vi bruker VHDL i dette faget for å beskrive digitale systemer. VHDL står får VHSIC(Very High Speed Integrated Cicuit) Hardware Description Language. VHDL er ikke case sensitive. VHDL brukes til kretsysntesisering (konstruksjon av kretser) og kretsimulering (testing av kretser). Første versjon av VHDL var VHDL 87. VHDL brukes for blant annet CPLDS (Complex Programmable Logic Devices) og FPGA (Field Programmable Gate Arrays).

Et typisk logikkelement i en FPGA består av: - en oppslagstabell (LUT) - et register - et register for å velge mellom de tidligere nevnte enhetene - en adderer (vansligvis)

Oppslagstabell (LUT)

Oppslagstabellen, LUT(LookUp Table) brukes til å implementere logiske funskjoner, altså kombinatoriske kretser. En "LUT" (lookup table) er en oppslagstabell som er en realisering av et kombinatorisk utrykk hvor hvert ord i Oppslagstabellen / minnet angir utgansverdien, og hvor inngangsverdiene velger riktig bit-verdi ved hjelp av en multiplexerstruktur. Det er genrelt sett antall innganger(bit) som bestemmer mengden LUTs for kombinatoriske kretser. Ikke kompleksiteten til systemet.

Minneceller (RAM) brukes for å "lagre" sannhetstabellen til en logisk funksjon. Adressen til minnet representerer inngangsverdier til funksjonen.

VHDL

Kodepraksis

Man tilorndet et signal og variabel henholdsvis slik:

Signal: <=, eks. sig <= 0;

Variabel: :=, eks. `var := 0;

Kodelinjer begynner med --, blokkommentarer er skrevet med /* */

`

Operander

- Highest precedence first, left to right within same precedence group, use parenthesis to control order.

- Unary operators take an operand on the right.

- "result same" means the result is the same as the right operand.

- Binary operators take an operand on the left and right.

- "result same" means the result is the same as the left operand.

** exponentiation, numeric ** integer, result numeric

abs absolute value, abs numeric, result numeric

not complement, not logic or boolean, result same

* multiplication, numeric * numeric, result numeric

/ division, numeric / numeric, result numeric

mod modulo, integer mod integer, result integer

rem remainder, integer rem integer, result integer

+ unary plus, + numeric, result numeric

- unary minus, - numeric, result numeric

+ addition, numeric + numeric, result numeric

- subtraction, numeric - numeric, result numeric

& concatenation, array or element & array or element, result array

sll shift left logical, logical array sll integer, result same

srl shift right logical, logical array srl integer, result same

sla shift left arithmetic, logical array sla integer, result same

sra shift right arithmetic, logical array sra integer, result same

rol rotate left, logical array rol integer, result same

ror rotate right, logical array ror integer, result same

= test for equality, result is boolean

/= test for inequality, result is boolean

< test for less than, result is boolean

<= test for less than or equal, result is boolean

> test for greater than, result is boolean

>= test for greater than or equal, result is boolean

and logical and, logical array or boolean, result is same

or logical or, logical array or boolean, result is same

nand logical complement of and, logical array or boolean, result is same

nor logical complement of or, logical array or boolean, result is same

xor logical exclusive or, logical array or boolean, result is same

xnor logical complement of exclusive or, logical array or boolean, result is same

Tatt fra University of Maryland. En annen nyttig kilde.

Designflyt i VHDL

-

Analyse og bearbaiding: Koden sjekkes for feil og skaper en representasjon på RTL-nivå

-

Simulering: Test at kretsen oppfører seg som den skal

-

Syntese: Oversettelse til kretsrepresentasjon

-

Place and Route (P&R): Implementasjon, kretsen tilpasses enheten som skal brukes (De10-Lite)

-

Timing analyse

-

Programmering

-

test på hardware(HW)

Oppbygning av et VHDL-design

Illustrasjon som viser et VHDL-design delt opp i pakker, grensesnitt(enitity) og kretsbeskrivelse(architecture).

Entity

entity ports: IN, OUT, INOUT(bicirectional) eller BUFFER, skal man bruke signalet internt i koden

Generic

Kan hjelpe med å gi bedre organisering i koden, gjøre koden mer lesbar og gjenbrukbar.

Verdien for en generic vil være den som er angitt i generic map init., dvs. 4 ns. hvis denne ikke er spesifisert, vil generic i Component-deklarasjonen benyttes (2ns), og hvis denne heller ikke er definert brukes generic i entiteten. (3ns)

Hvilken verdi for gc_gate_delay kommer til å bli brukt på XOR-porten? Begrunn svaret.

entity xor2 is

generic (gc_gate_delay : time := 3 ns);

port (

In1, In2 : in std_logic;

z : out std_logic);

end entity xor2;

architecture behavioural of xor2 is

begin

z <= (In1 xor In2) after gc_gate_delay;

end architecture behavioural;

architecture structural of half_adder is

component xor2 is

generic (gc_gate_delay : time := 2 ns);

port (

In1, In2 : in std_logic;

z : out std_logic);

begin

i_xor2 : xor2

generic map (gc_gate_delay => 4 ns)

port map (

In1 => x, In2 => y, z => sum);

end architecture structural;

Architecture

F ormålet med en "architecture" i VHDL er å beskrive den interne implementeringen av en komponent.

Samtidige versus sekvensielle kodesetninger

Et viktig prinsipp i maskinvarebeskrivende språk, inklusive VHDL, er samtidighet. - I digitale kretser foregår alt samtidig. - Dette er reflektert i VHDL ved at kodesetninger kan skrives i den rekkefølgen man ønsker. - Men et gitt signal kan kun få en verdi én gang. - Unntak: Visse kodestrukturer (prosesser og subprogrammer) tolkes linje for linje, men er alltid samtidige i relasjon til resten av koden.

Processes are concurrent with respect to all other statements, but internally a process is sequential (only statements in (b)). Statements are inherently concurrent (parallels)sequential inside PROCESS, FUNCTION or PROCEDURE.

Select (samtidig)

Eksempel: multiplexer, der sel er av typen natural.

with sel select

y <= a when 0,

b when 1,

c when 2,

d when others;

Man har også matching select statement select?som bruker matching equality operator ?=, som er nyttig når man har en sannhetstabell som inkluderer "don't care"-verdier.

When (samtidig)

target <= value when condition else

value when condition else

value;

- har priority encoding (for sannhetstabeller bruker man slect)

- slutter med else, og garanterer at det ikke blir en latch.

Eksempel med multi-bit tri-state buffer):

outp <= inp when ena = '1' else

(others => 'Z');

Generate (samtidig)

- for-generate (most used)

- if-generate

- case-generate.

- For-generate: Acts as a loop where a piece of hardware is inferred for every time.

Process (sekvensiell)

- Internally sequential (mini program).

- Each process is concurrent with respect to all other statements.

- Must be used when constructing sequential cicuits, but can also be used for combinatorial circuits.

- Procedures and functions are sequential

- Sequential statements allowed in processes:

- If (sequential version of when)

- Case (sequential version of select)

- Loop (sequential version of generate)

- Wait

If (sekvensiell)

Den sekvensielle versjonen av when, som er samtidig. - har priority encoding - Alle kombinasjoner må dekkes for å unngå latches i kombinatorisk logikk. - Ingen handling på if-setning -> unaffected eller null

Case (sekvensiell)

Den sekvensielle versjonen av select, som er samtidig.

- Brukes mest til å implementere en sannhetstabell

- Har ingen priotiry-encoding (sammenlignet med if)

- Ingen handling på case statement -> unaffected eller null

[label:] case expression is

when choice => assignments;

when choice => assignments;

when others => assignments;

end case;

Loop (sekveniell)

Den sekvensielle versjonen av generate, som er samtidig.

- Kan bare brukes i prosesser og subprogrammer

- loop (unconditional, simulation only)

- while-loop (simulation only)

- for-loop (most frequently used for synthesis)

- loop with exit

- loop with next

- For synthesis: The range must have static bounds.

Objektklasser i VHDL

Et objekt er en enhet som har en verdi av en datatype. Det er fire objeklasser i VHDL.

- Constant: Only readable, cannot be changed.

- Signal: Used for signaling between processes.

- Variable: Only for internal use in a process, procedure or function.

- File: Only used in testbenches (not hardware).

Signal

- Capable of passing values in and out of the circuit or between internal parts (wires).

- Declared (created) in the declaration part of entity, architecture, package, generate or block.

signal signal_name: signal_type [:= default_value];

Remark: Default value for signals should be avoided in code for synthesis (reset- signal should be used to initialise registered signals).

Variable

- Only used in sequential code.

- Declared (created) in processes and functions/procedures.

- Updated immediately.

- Initial value optional, but more meaningful than for signals.

- Do not use shared variable (use signals instead).

variable variable_name: variable_type [:= initial_value];

variable count: natural range 0 to 2**NUM_BITS-1;

count := count + 1;

Signal versus variabel

Signaler kan deklareres i en arkitektur (mellom architecture og begin), mens variabler må deklareres i en prosess (mellom process og begin eller lokalt i en funksjon/prosedyre (shared variables kan deklareres som signaler). For tilordning av signaler brukes <=, og for variabler brukes:=. Signaler oppdateres etter en prosess har blitt kjørt dvs. den bruker gammel verdi i prosessen ny verdi ble tilorndet. Variabler oppdateres med en gang, dvs. ny verdi benyttes etter ny verdi er blitt tilordnet. Signaler endrer ikke verdi før hele prosessen er kjørt, og kan brukes mellom prosesser/globalt. Variabler endrer verdi med en gang, og kan bare brukes lokalt i en prosess, og kan ikke returneres.

Datatyper

- VHDL: Strongly typed language.

- Does not allow data transfer between objects of different types (even if they are identically declared).

- Appropriate casting functions must be used.

- Does not allow implicit type conversion.

- Every operator is constructed for specific data types.

- Types can be predefined or user-defined.

- Det er tillatt å definere egne datatyper i VHDL

- Det er ikke mulig å definere signaler med typen real ved syntese av hardware

- Dataypen biter definert av '0' og '1'. Merk at

std_logichar flere definisjoner. - Boolean → 1 bit

- Integer → 64 bit/32 bit

Klasser av datatyper

- Scalar (integers, enumaration types, floating point, physical)

- Composite (array/record)

- Access (simulation only)

- File (simulation only)

- Proteced (simulation only)

std_logic

To viktige datatyper å bite seg merke i er std_logic og std_ulogic. Begge kan representere følgende verdier

| Verdi | Forklaring |

| ‘1’ | Logisk 1 |

| ‘0’ | Logisk 0 |

| ‘Z’ | Høy impedans |

| ‘W’ | Svakt signal, ukjent |

| ‘L’ | Svak 0, pulldown |

| ‘H’ | Svak 1, pullup |

| ‘-‘ | Don’t care |

| ‘U’ | Uninitialisert |

| ‘X’ | Ukjent, flere drivere |

Les mer om forskjeller og likheter mellom std_logicog std_ulogicpå VHDLWhiz sin side om disse datatypene.

Aggregation and concatenation

- Putting data pieces together to form or enlarge data arrays.

signal s1, s2, s3, s4: std_logic_vector(3 downto 0);

s1 <= ('1','0','1','0') -- Aggregation: s1="1010"

s2 <= ('1','0',others => 'Z'); -- Aggregation: s2="10ZZ"

s3 <= "11" & "00"; -- Concatenation: s3="1100"

s4 <= '1' & s3(3 downto 1); -- Concatenation: s4="1110"

Sub-programmer

Funksjon

- Will always return a single object of a specified data type calculated

- based on a given set of input parameters.

- Will always create combinatorial logic.

- Can be:

- Pure: does not rely on external objects and will always yield same results with same parameters.

- Impure: can access external objects and give different results with the same parameters.

- Navn: Må følge reglene for VHDL-identifikatorer.

- Input-liste: Kan inneholde et vilkårlig antall parametere.

- De kan ha klassene konstant (som standard), signal eller fil (variabel er ikke tillatt).

- Returnerer alltid ett objekt, returtypen må spesifiseres.

- Må alltid være del av et komplett uttrykk.

- Deklarativ del: Typisk for interne variabler.

- Kodesetninger: Kun sekvensielle (som i prosess), men ikke støtte for wait.

- Syntese av funksjon → kombinatorisk logikk

Ren(pure) funksjon: - Returnerer alltid samme resultat for samme parametre. - Avhenger ikke av eksterne objekter (signaler eller variabler). Uren(impure) funksjon: - Kan returnere ulike resultater selv med samme parametre. - Kan ha tilgang til eksterne objekter (f.eks. filer). - Ikke anbefalt for syntese.

Prosedyre

- Hovedforskjell til funksjoner: Kan ha flere utgangsverdier

- Kan håndtere tid (wait-kodesetninger).

- Kan lese fra/skrive til filer (nyttig i testbenker/simulering).

-

For syntese: Vanligere å bruke funksjoner enn prosedyrer

-

Navn: Må følge reglene for VHDL-identifikatorer.

- Input/output-liste: Kan inneholde objekter av alle klasser (konstant, signal, variabel, fil).

- in: konstant (default), signal, variabel.

- out/inout: signal, variabel (default).

- Filer har ingen modus.

- Objektklassen gjelder kun lokalt i prosedyren, ikke i kallende enhet.

- Kan håndtere tid

- Nyttig i testbenker.

- Egenstående kodesetninger

- Er ikke del av et uttrykk.

Forskjeller og likheter mellom funskjoner og prosedyrer

| Egenskap | Funksjon | Prosedyre |

| Bruksområder | Forenkle vanlige operasjoner, repeterende kode | Løsninger som krever flere utgangsverdier(simulering) |

| Input/output | Ubegrenset input, en output | Ubregrenset input og output, inkl bidirectional |

| Støtte for tid | Ingen støtte for tid(wait) | Støtte for wait og fil |

| Kall | Kalles som en del av et utrykk | Kalles som en selvstendig kodesenting |

| Subprogramkall | I både samtidig og sekvensiell kode | I både samtidig og sekvensiell kode |

Pakker

- Collection of functions/procedures.

- As well as types/constants.

- "package" er en sammensetning av relaterte funksjoner, prosedyrer og dekorasjoner.

- library → collection of FUNCTIONS, PROCEDURES and COMPONENTS in PACKAGES.

LIBRARY ieee;

USE ieee_std_logic_1164.all;

- Samling av deklarasjoner (for eksempel funksjoner og prosedyrer) som er felles for en modell.

- Kan være forhåndsdefinert eller brukerdefinert.

- use

ieee.numeric_std.all;er f.eks. forhåndsdefinert. Formål: - Unngå å skrive den samme kode om og om igjen.

- Bedre organisering og enklere kode.

- Kan gjenbrukes i andre prosjekter. Pakker består av:

- Pakkedeklarasjon

- Pakkeinnhold (innmaten)

Tilstandsmaskiner

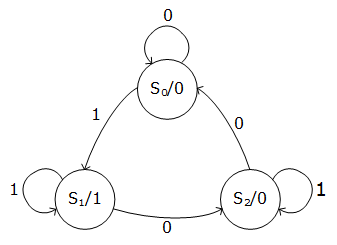

En tilstandsmaskin kan besrkives som en case-setning i en kombinatorisk proseess. Man kan også implementere tilstandsmaskiner som en klokket prosess.

Moore

I Moore-tilstandmaskiner er utgangen av tilstandsmaskinen bare avhengig av den nåværede tilstanden til tilstandsmaskinen. Input påvirker bare overganger mellom ulike tilstander.

Mealy

I Mealy-tilstandsmaskiner er utgangen avhengig av både den nåværende tilstanden og og input. (Output endres med overganger mellom tilstander, ikke selve tilstanden.)

Hovedforskjeller Moore og Melay

| Egenskap | Moore | Mealy |

| Utganger avhenger av | nåværende tilstand | Nåværende tilstand og inngangsverdi |

| Utgang endres ved | Tilstander | Overganger |

| tall tilstander | Gjerne flere | Gjerne færre |

| sponstid | Tregere(output etter tilstand) | Raskerer(output i overgang) |

| Kompleksitet | Enklere utgangslogikk | Litt mer kompleks utgangslogikk |

(Tatt fra Scott Davis (2025))

Eksempler på tilstandsmaskiner (klokket og kombinatorisk)

Entityen og arkitekturen kan deklareres likt. I arkitekturen definerer man en egen type for de ulike tilstandene, og bruker et signal for å lagre tilstandsverdien.

Klokket prosess

- blir triggret på reset og stigende klokkeflanke.

- lagrer neste tilstandsverdi.

Kombinatorisk prosess

- regner ut neste state basert på nåværende tilstand.

Testbenker

Testbenker er VHDL-kode som verifiserer at kretsimplementasjonen (DUV/DUT (Device under Verification/Test)) beskrevet av VHDL-kode har ønsket opprsel.

'

'

Oppgavene til en testbenk er som følgende:

- Skap stimuli på inngangen til systemet (DUV/DUT)

- Sammenlign responsen fra DUV/DUT med fasit

- Rapporter resultatene fra verifikasjonsprosessen.

Man kan teste med en funskjonell simulasjon, som er uten delays, eller med en timing simulation som inkluderer propagasjonsdelay. Det er mulig å gjøre simulering både med og uten de interne tidsforsinkelsene i en FPGA-krets.

Assert

- Main purpose: Checking the design.

- Used in testbenches.

- Does not infer any hardware.

- Can be used in both sequential and combinatorial code.

- The message (static and/or dynamic) is displayed when the condition is false.

[label:] assert condition [report message] [severity level];

Alvorlighetsgrad (severity level)

- En assert kan ha forskjellige nivå av alvorlighet:

- Note: For informasjonsdeling

- Warning: Noe unormalt ble oppdaget.

- Error: En feil er oppdaget (standardgraden)

- Failure: En bug i koden.

- Ved failure stoppes simuleringen, så dette kan brukes for å avslutte testbenken:

- Det er du som designer og tester som spesifiserer alvorlighetsnivået. assert false report "Testbench finished" severity failure;

Notat: Man kan i VHDL 2008 også bruke finish som kommando for å avslutte testbenken, men dette tror jeg ikke er nevnt i pensum.

Det er ofte ønskelig med dynamiske verdier i report-delen av asserten. Da kan to_string brukes for å konvertere tallverdier til en streng. Strenger kan konkatineres med &.

assert actual_value = expected_value

report "Actual value does not match expected value at t=" & to_string(now) & "."

severity error;

Notat: det er ikke tatt for seg lesing og skriving til fil samt textio i dette kompendiumet da det anses som lite relvant for eksamen, og er mer som ekstra tilleggskunnskap.

I dette eksempelet vil "Dette er en test… Verdi = 10 meter" skrives til filen out.txt. For å skrive til konsoll istedenfor fil: writeline(output, v_buf);

Dealing with Time in VHDL

-

Major difference between code for synthesis and simulation: The presence of time in the latter.

-

Useful constructions for testbenches related to time:

-

wait forThe process waits for a specific time. -

afterAn action is scheduled after a specific time. -

nowReturns the current simulation time. -

S'stable(t)Attribute, returns true if no events have occured on signal S during the last t time units (looks backwards). -

S'last_eventAttribute, returns the time since last event on S.

-S'transaction Attribute, causes a bit to toggle when a transaction (future event) on signal S is scheduled.

Eksempler på enkle utrykk

Systemet beskrevet i wait-utrykk:

p_test1: process is

begin

test1 <= '1';

wait for 20 ns;

test1 <= '0';

wait for 10 ns;

end process p_test1;

p_test2: process is

begin

test2 <= '0';

wait for 30 ns;

test2 <= '1 ';

wait;

end process p_test2;

Greit å vite

Sekvensiell logikk versis kombinatorisk logikk

Digtital logikk har to hovedkategorier; kombinatoriske logikk, hvor endringer skjer umiddelbart, og klokket logikk, hvor endringer ved en klokkeflanke. Klokket logikk kalles også for sekvensiell logikk. Forskjellen mellom klokket logikk og kombinatorisk logikk er at klokket logikk inneholder minne i form av vipper, dermed er det ikke nødvendig i koden å tilordne alle signalene for hver gang, slik som i kombinatorisk logikk. Klokket logikk er avhengig av systemets tidligere verdier/tilstander. Klokket logikk er bygget opp av vipper (flip-flops), som oppdaterer utganger på hver flanke av et klokkesignal. Kombinatorisk logikk realiseres med logiske porter. Kombinatorisk logikk krever ingen kunnskap om systemets tidligere tilstand, mens sekvensiell logikk er avhengig av å vite systemets tidligere tilstand.

Latcher og flip-flops

- Latches og flip-flops er "registre". De er enheter for å lagre informasjon.

- Latches → level-sensitive, transparent when clk is high, opaque when clk is low.

- Flip-flops → edge-sensitive, transparent at clock transitions

Om man skal ha en kombinatoriske krets uten en latch må man forsikre seg om at variabler alltid tilordnes en verdi i eller før en if-setning, eller inkludere en "else" i koden. Om en variabel brukes for den blir tilegnet i prosessen må man legge til et registerelement for å huske forrige verdi av variabelen. Lag en tabell for å sjekke om alle signal i en if-løkke blir tildelt en verdi!

- A signal must always be assigned a value in concurrent processes or else latches will be inferred (combinatorial loops).

- Make sure to use others and remember that

std_logichas more possible values than ‘0’ and ‘1’. - We don’t want latches.

- If using the if statement in a process all combinations must be covered for concurrent logic.

- Not necessary for sequential logic.

- Do not use unaffected in combinatoric logic → Latches

Litt om metastability og glitches

- Metastability → when data changes in the forbidden time interval (flip-flops)

- Requirement: Data-signal must be stable a time tsetup before the clock edge and a time thold after the clock edge.

- Metastability (undefined voltage or illegal digital state) can occur if the timing requirements are violated.

- Use two-flop synchronizer to avoid metastability: The synchronizer introduce extra latency.

- Glitches → caused by propagation delays

- A glitch can occur in a combinatoric circuit when there is a race between two (or more) signal paths.

- In a synchronized system: Glitches can only occur immediately after the clock transistions (usually not a problem as long as the output is not used as a clock).

- Avoid glitches: Use different clock edges, synchronize the outputs from a combinatorial circuit with flip-lops.

Sensitivitetslister og wait-utrykk

En sensitivitetsliste er en opplisting av de signalene som prosessen skal reagere på. Prossesen kjøres når det skjer en endring i signalene i sensitivitetslisten. I f.eks Quartus Prime Lite kan syntetiseringen gjenkjenne mangler i sensitivitetslisten og legge de til, mens i en simulering vil dette skape feil. Dette er gjerne noe man må være obs på når man får en oppgaver som beskriver et system som oppfører seg ulikt i syntese versus simulering.

wait: prosessen venter på at wait-betingelsen skal bli oppfylt, og må dermed være første instruks/kommando i prosessen. Med sensitiversliste kan man lage en kombinasjon av kombinatorisk og klokket logikk. Dette kan man ikke gjøre med wait-utrykk.

When there is a change (event) on at least one signal in the sensitivity list: - The process is executed. - Once started, the process runs to completion (to the end process statement).

An alternative to sensitivity list: - Use a wait statement (responsible for starting the execution of the process), must be the first statement if writing code for synthesis. - The process runs to completion, and stops at the wait statement (process suspends until the wait statement again is true).

Heksadesimal

Heksadesimal er et tallsystem som inneholder 16 ulike måter å representere tall på, 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F. Dette kalles et base-16 system.

Desimal 15 beskrives dermed som heksadesimal F. Når man skal beskrive f.eks 16 eller 17, begynner man på nytt i heksidesimalrekken, med 10(deismal 16) og 11(desimal 17).

Desimal 15 kan beskrives som '1111' i binær, og dette gjør at heksadesimal brukes som en metode for å forkorte utrykk i binær. Dette er mye brukt for å analysere signaler for å spare plass og skrive kortere.

I VHDL kan man skrive et heksadesimaltall som X"AD", som er lik den mer vanlige navnekonvensjonen i C, 0xAD.

Dekoding av heksadesimal til binær var et eksamenspørsmål fra et tidligere lignende fag, og måten man gjør det er som følgende:

Man deler opp tallet "AD" i hver sin del, A og D. Disse kan man så bruke til å konvertere til desimaltall, 10 og 13. representerer man 10 i binær, får man 1010 (8 + 2), og representer man 13 i binær får man 1101 (8 + 4 +1). Dette kan så settes sammen til "10101101", som er det binære tallet.

Beksrivelse av et system

Når man skal beskrive et system, husk klokke og reset. Tenk på overflow/mente ut! Når man beskriver en entity ut i fra et grensesnitt, vær obs på antall bit på hvert signal.

Oppdag klokkeflanker

- Both work for synthesis, but the rising_edge/falling_edge are recommended because:

- Checks the value before and after the clock transition.

- Works also for 'L' and 'H' values (converted to '0' and '1').

- Works also for data types bit and boolean.

if clk'event and clk = '1' then … -- Positiv clock transition

if clk'event and clk = '0' then … -- Negative clock transition

if rising_edge(clk) then … -- Positiv clock transition (recommended)

if falling_edge(clk) then … -- Negative clock transition (recommended)

Avoid Multiple Assignements to a Signal

- Not allowed to assign a value to a signal from several places.

- Concurrent code: Only possible to assign a signal one place, or inside one combinatoric process.

- Sequential code: A signal can be assigned several times, but only inside the same process.

Suggested Procedure for Aritmetic Circuits

-

- If the circuit is aritmetic: Integer or floating point?

- Floating point should be avoided in VHDL due to higher usage of resources, higher power consumption and lower speed.

-

- List all operations involved (+, -,

*, /,**, rem, mod, abs) and check the constraints for each operator to be used:

- List all operations involved (+, -,

- Types (unsigned or signed).

- Number of bits in the result.

-

- How to deal with overflow:

- Extend the operands. •-Flag (must decide how to handle a flag).

Aritmetic Circuits in the VHDL code

-

Use only standard-logic datatypes for the circuit ports.

-

In the architecture: Convert the standard-logic vector to one of the arithmetic datatypes.

-

Do the computations.

-

Convert the results back to standard-logic vector on the ports.

-

Carefully simulate the design.

Component Instantiation Statements

- Declaration of the component (identical with the entity).

component component_name [is]

[generic (…);]

port (…);

end component [component_name];

- A component instantiation statement.

label: [component] component_name

[generic map (generic_assosciation_list)]

port map (port_association_list);

Andre notater

I dette kompendiumet brukes sekvensiell(sequential) vs samtidig(concurrent) og kombinatorisk(combinatoric) vs klokket(clocked) logikk litt om hverandre.

Samtidig(concurrent) og sekvensiell(sequential) kode beskriver hvordan VHDL-koden kjører, mens kombinatorisk(combinatoric) og sekvensiell(sequential) logikk beksirver oppførselen til hardwaren som koden beskriver. Dette er ikke gitt veldig konsekvent i teksten, så vær obs på dette.

Tips til eksamen

- Øv på tildigere eksamener, se gjennom øvinger og ERT-økter og gjør oppgaver fra boka.